# Kodak Digital Science<sup>TM</sup> KAC – 1310 1280 x 1024 SXGA CMOS Image Sensor

#### **Features**

- ½" Color SXGA Advanced CMOS Image Sensor

- 1280 x 1024 active imaging pixels progressive scan

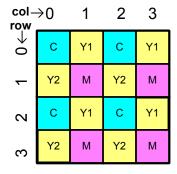

- Monochrome or Bayer (RGB or CMY) Color Filters

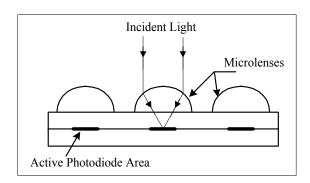

- 6.0μm pitch square pixels with microlenses

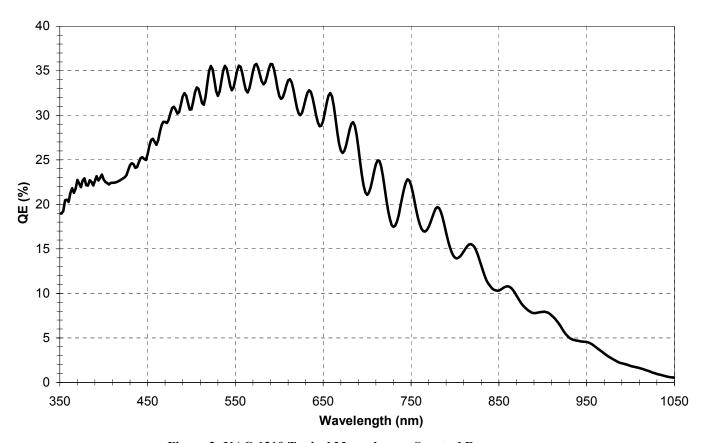

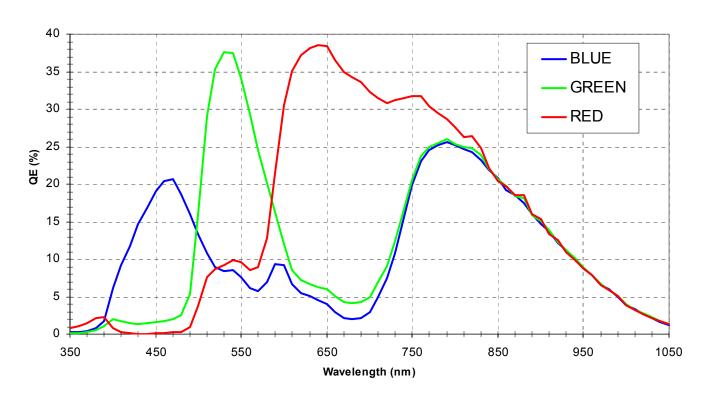

- Kodak patented pinned photodiode architecture; high blue QE, low dark current, lag free

- High sensitivity, quantum efficiency, and charge conversion efficiency

- True Correlated Double Sampling for low read noise

- Low fixed pattern noise and wide dynamic range

- Antiblooming control and Continuous variable speed rolling electronic shutter

- Single 3.3V power supply; Single master clock

- Digitally programmable via I<sup>2</sup>C compatible interface

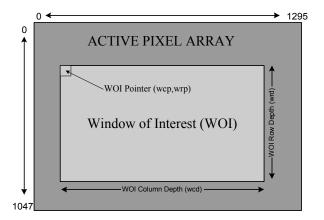

- Pixel addressability to support 'Window of Interest' windowing, resolution, and sub-sampling

- External sync signal for use with strobe flash

- On-chip 20x programmable gain for white balance and exposure gain

- 10-bit, pipelined algorithmic RSD ADC

- 15 fps full SXGA at 20MHz Master Clock Rate

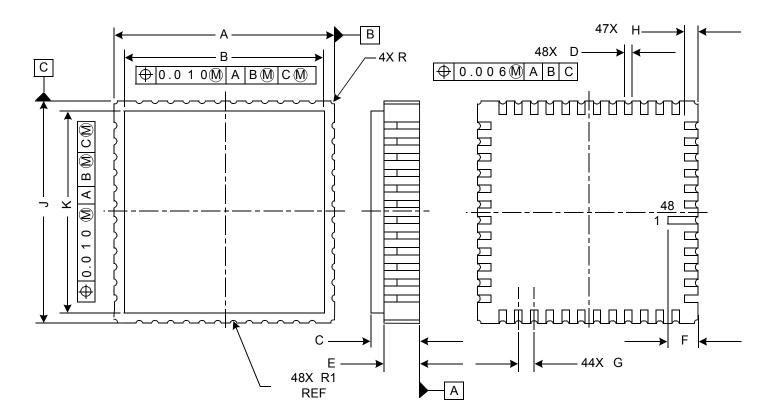

- 48 pin CLCC package

- Dark reference pixels with automatic Frame Rate Dark Clamp

- · Encoded Sync data stream

- Column offset correction circuitry

#### **Key Specifications**

• **Pixel size:** 6.0μm x 6.0μm

Resolution: 1280 x 1024 active

Image Size: 7.68mm x 6.14mm (~1/2")

• **ISO**: 180

Saturation Signal: 40,000 electrons

Scan Modes: Progressive Scan

Shutter Modes: Continuous and Single Frame

Rolling Shutter Capture

Maximum Readout Rate: 20 MSPS

Frame Rate: 0-15 frames per second

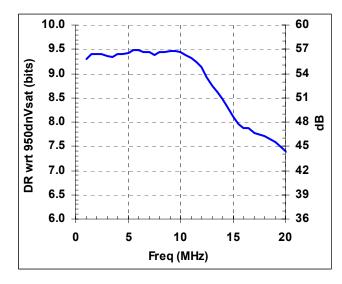

System Dynamic Range: 56dB (1 - 10 MHz);

48 dB (11 - 15 MHz); 44 dB (16 - 20 MHz)

• Response Non-Linearity: <2%, 0 – 90% Vsat

Programmable Gain Range:

Global: 7.5x, 0.02x steps

White Balance: 2.7x, 0.02x steps

• ADC: 10-bit, RSD ADC (DNL +/-0.5 LSB, INL

+/-1.0 LSB)

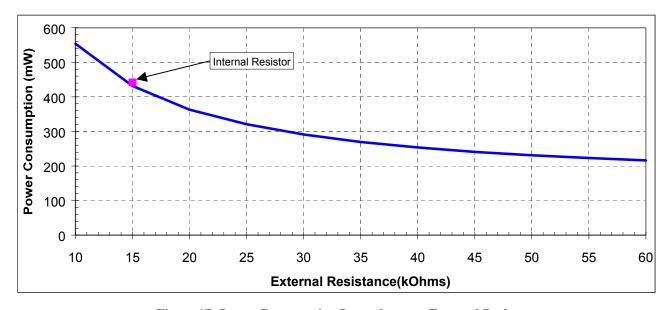

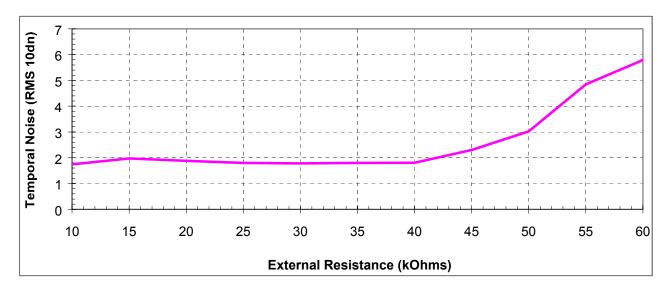

• Power Dissipation: <250mW (dynamic) /

25mW (standby)

Release Date: April 30, 2002

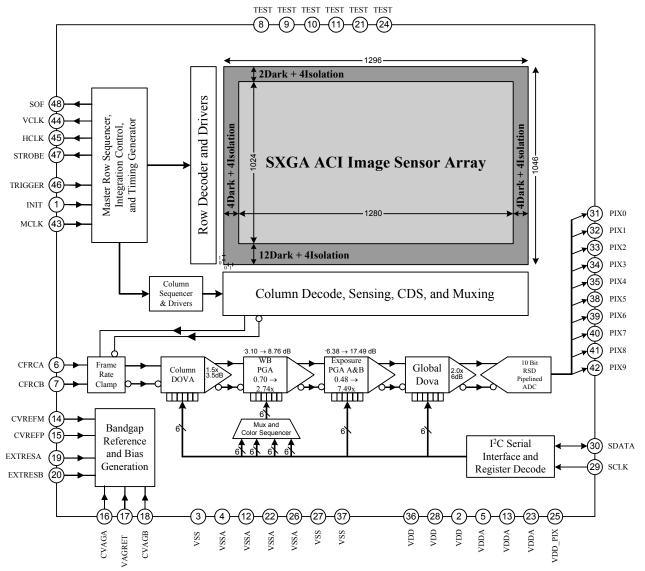

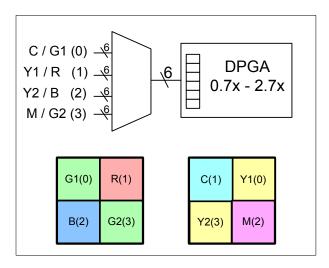

Figure 1: KAC-1310 Block Diagram

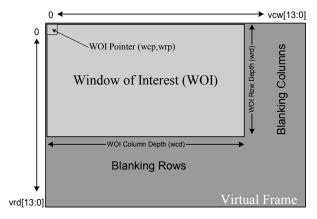

The KAC-1310 is a fully integrated, high performance  $\frac{1}{2}$ " optical format Megapixel CMOS image sensor including integrated timing control and programmable analog signal processing. This sensor provides system designers a complete imaging solution with a monolithic image capture and processing engine. System benefits enable design of smaller, portable, low cost and low power systems. Each pixel on the sensor is individually addressable allowing the user to control the "Window of Interest" (WOI), panning and zooming, sub-sampling, resolution, exposure, white balance, and other image processing features via a two pin  $I^2C$  compatible interface. This device runs from a single 3.3V supply and single master clock.

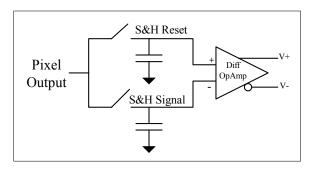

The imager uses Kodak's patented Pinned Photodiode CMOS active pixels. The 6.0µm pixel design provides true correlated double sampling for low read noise operation, high quantum efficiency, low dark current, and no image lag. Kodak's patented pixel design combined with low noise mixed signal circuits provides a high sensitivity, low noise integrated "camera on a chip".

#### **Eastman Kodak Company - Image Sensor Solutions**

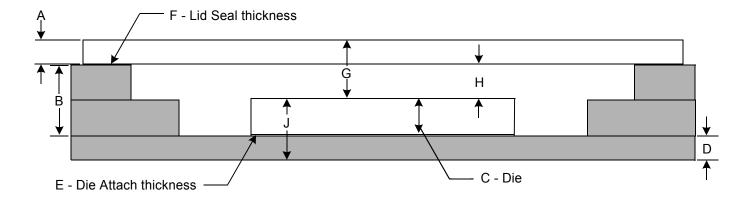

#### **Table 1: KAC-1310 Pin Definitions:**

|    | Pin<br>Name | Description                       | Pin<br>Type | Power | Value        | Pin<br>No. |         | Description                           | Pin<br>Type | Power | Value                  |

|----|-------------|-----------------------------------|-------------|-------|--------------|------------|---------|---------------------------------------|-------------|-------|------------------------|

| 1  | INIT        | Sensor Initialize                 | I           | D     |              | 25         | VDD_PIX | Pixel Array Power                     | P           | A     | 3.3 V                  |

| 2  | VDD         | Digital Power                     | P           | D     | 3.3 V        | 26         | VSSA    | Analog Ground                         | G           | A     | 0 V                    |

| 3  | VSS         | Digital Ground                    | G           | D     | 0 V          | 27         | VSS     | Digital Ground                        | G           | D     | 0 V                    |

| 4  | VSSA        | Analog Ground                     | G           | A     | 0 V          | 28         | VDD     | Digital Power                         | P           | D     | 3.3 V                  |

| 5  | VDDA        | Analog Power                      | P           | A     | 3.3 V        | 29         | SCLK    | I <sup>2</sup> C Serial Clock Line    | I/O         | D     | $3.3 \mathrm{k}\Omega$ |

| 6  | CFRCA       | Frame Rate Clamp Capacitor A      | О           | A     | 0.1µF        | 30         | SDATA   | I <sup>2</sup> C Serial Data Line     | I/O         | D     | $3.3 \mathrm{k}\Omega$ |

| 7  | CFRCB       | Frame Rate Clamp Capacitor B      | O           | A     | $0.1 \mu F$  | 31         | PIX0    | Output Bit 0=1 <sub>10</sub> Weight   | O           | D     |                        |

| 8  | TST_VRO     | Analog Test Reference Output      | O           |       |              | 32         | PIX1    | Output Bit 1=2 <sub>10</sub> Weight   | O           | D     |                        |

| 9  | TST_VSO     | Analog Test Signal Output         | О           |       |              | 33         | PIX2    | Output Bit 2=4 <sub>10</sub> Weight   | О           | D     |                        |

| 10 | TST_VRI     | Analog Test Reference Input       | I           |       |              | 34         | PIX3    | Output Bit 3=8 <sub>10</sub> Weight   | О           | D     |                        |

| 11 | TST_VSI     | Analog Test Signal Input          | I           |       |              | 35         | PIX4    | Output Bit 4=16 <sub>10</sub> Weight  | О           | D     |                        |

| 12 | VSSA        | Analog Ground                     | G           | A     | 0 V          | 36         | VDD     | Digital Power                         | P           | D     | 3.3 V                  |

| 13 | VDDA        | Analog Power                      | P           | A     | 3.3 V        | 37         | VSS     | Digital Ground                        | G           | D     | 0 V                    |

| 14 | CVREFM      | ADC Bottom Bias Ref Capacitor     | O           | A     | $0.1\mu F$   | 38         | PIX5    | Output Bit 5=32 <sub>10</sub> Weight  | О           | D     |                        |

| 15 | CVREFP      | ADC Top Bias Ref Capacitor        | O           | A     | $0.1 \mu F$  | 39         | PIX6    | Output Bit 6=64 <sub>10</sub> Weight  | O           | D     |                        |

| 16 | CVAGA       | Common Mode Capacitor Input       | О           | A     | $0.1 \mu F$  | 40         | PIX7    | Output Bit 7=128 <sub>10</sub> Weight | О           | D     |                        |

| 17 | VAGRET      | Return for VAG external caps      | О           | A     |              | 41         | PIX8    | Output Bit 8=256 <sub>10</sub> Weight | О           | D     |                        |

| 18 | CVAGB       | Common Mode Reference Capacitor   | O           | A     | $0.1 \mu F$  | 42         | PIX9    | Output Bit 9=512 <sub>10</sub> Weight | О           | D     |                        |

| 19 | EXTRESA     | External Bias Resistor            | I           | A     | 39k Ω        | 43         | MCLK    | Master Clock = Pixel Rate             | I           | D     |                        |

| 20 | EXTRESB     | External Bias Resistor            | I           | A     | $39k \Omega$ | 44         | VCLK    | Line Sync                             | O           | D     |                        |

| 21 | NC          |                                   |             |       |              | 45         | HCLK    | Pixel Sync                            | О           | D     |                        |

| 22 | VSSA        | Analog Ground                     | G           | A     | 0 V          | 46         |         | Sensor Trigger Signal                 | I           | D     |                        |

| 23 | VDDA        | Analog Power                      | P           | A     | 3.3 V        | 47         | STROBE  | External Sync for Strobe Flash        | О           | D     |                        |

| 24 | TST_INJ     | Pixel Row 1046./1047 Inj Bbias In | I           |       | 3.3 V        | 48         | SOF     | Start of Frame Sync                   | 0           | D     |                        |

#### Legend:

P = VDD

G = VSS

I = Input

O = Output

D = Digital

A = Analog

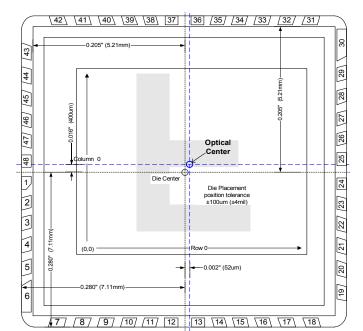

Figure 2. Pinout Diagram

## Kodak Digital Science KAC-1310 CMOS Image Sensor

#### **Table Of Contents**

| 1.0     | Overview                                             |   |

|---------|------------------------------------------------------|---|

| 2.0     | Sensor Interface                                     |   |

| 2.1     | Pixel Architecture                                   |   |

| 2.2     | Color Filters and Lenslets                           | 1 |

| 2.3     | Frame Capture Modes                                  |   |

| 2.3.1   | Continuous Frame Rolling Shutter Capture Mode (CFRS) |   |

| 2.3.1.1 | CFRS Video Encoded Data Stream                       |   |

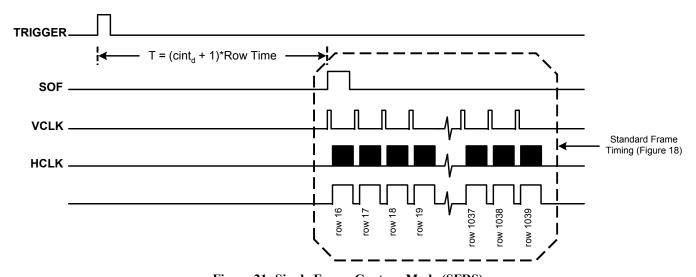

| 2.3.2   | Single Frame Rolling Shutter Capture Mode (SFRS)     | 1 |

| 2.3.3   | Window of Interest (WOI) Control                     | 1 |

| 2.3.4   | Sub-Sampling Control (Resolution)                    | 1 |

| 2.4     | Virtual Frame                                        | 1 |

| 2.5     | Integration Time                                     | 1 |

| 2.5.1   | CFRS Integration Time                                | 1 |

| 2.5.2   | SFRS Integration Time                                | 1 |

| 2.6     | Frame Rate                                           | 1 |

| 2.6.1   | CFRS Frame Rate                                      |   |

| 2.6.2   | SFRS Frame Rate                                      | 1 |

| 3.0     | Analog Signal Processing Chain (ASP)                 | 1 |

| 3.1     | Correlated Double Sampling (CDS)                     |   |

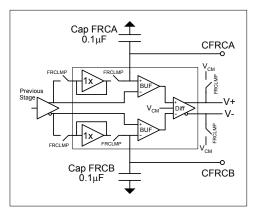

| 3.2     | Frame Rate Clamp (FRC)                               |   |

| 3.3     | Column Digital Offset Voltage Adjust (CDOVA)         |   |

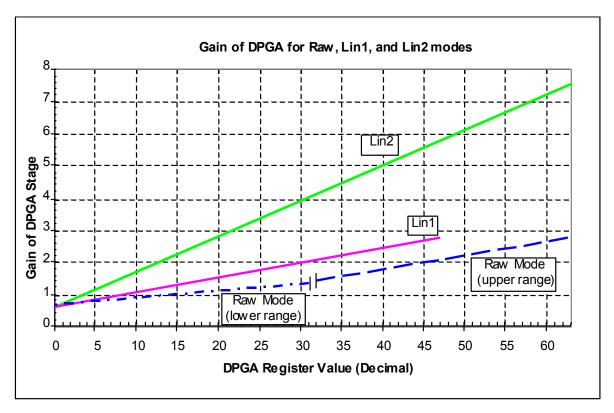

| 3.4     | Programmable Gain Amplifiers (PGA)                   |   |

| 3.4.1   | Gain Modes                                           | 1 |

| 3.4.2   | White Balance Control PGA (WB Gain)                  |   |

| 3.4.3   | Exposure Gain PGA (Exp Gain A/B)                     | 1 |

| 3.5     | Global Digital Offset Voltage Adjust (GDOVA)         |   |

| 3.6     | Analog to Digital Converter (ADC)                    |   |

| 4.0     | Additional Operational Conditions                    |   |

| 4.1     | Initialization (Standby Mode)                        | 1 |

| 4.2     | Standby Mode                                         |   |

| 4.3     | Output Tristate                                      |   |

| 4.4     | Readout Order                                        |   |

| 4.5     | Readout Speed                                        |   |

| 4.6     | Internal Bias Current Control                        |   |

| 5.0     | Waveform Diagrams                                    |   |

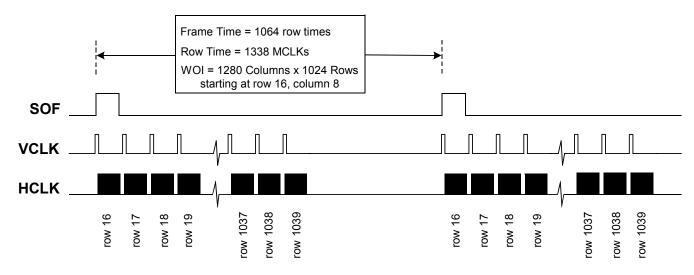

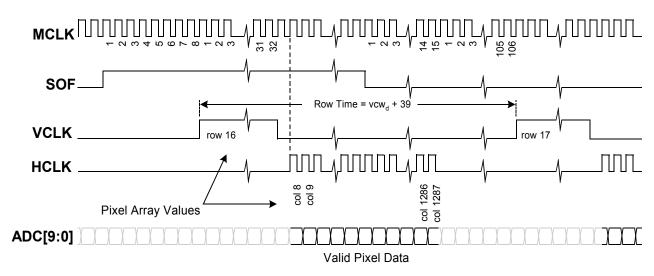

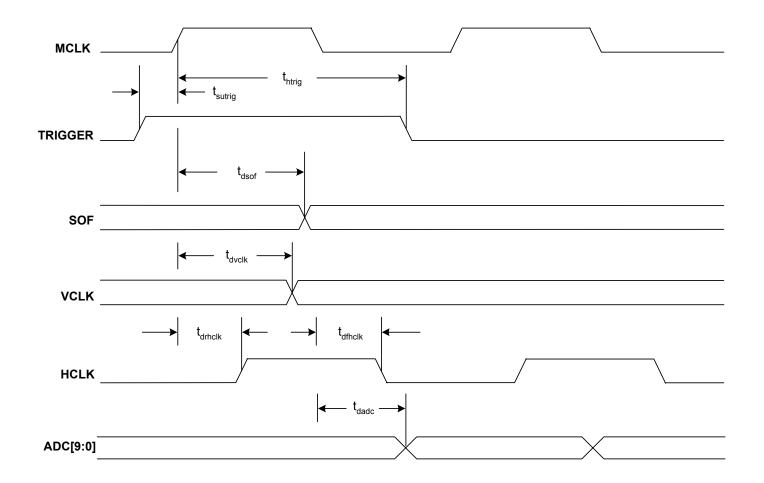

| 5.1     | Start of Row Readout (SOF)                           | 2 |

| 5.2     | Horizontal Data Sync (VCLK)                          | 2 |

| 5.3     | Data Valid (HCLK)                                    | 2 |

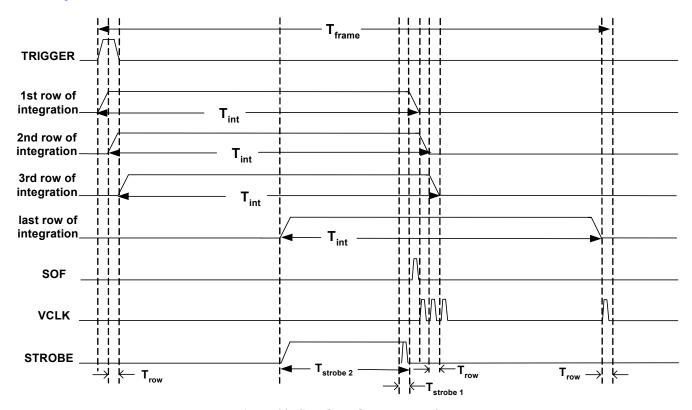

| 5.4     | Strobe Signal                                        | 2 |

| 6.0     | Register List Reference                              | 2 |

| 7.0     | Detailed Register Block Assignments                  | 2 |

| 7.1     | Color Gain Registers $00_h \rightarrow 03_h$         | 2 |

| 7.2     | Reference Voltage Adjust Registers (0Ah, 0Bh)        | 2 |

| 7.3     | Power Configuration Registers (0C <sub>h</sub> )     | 3 |

| 7.4     | Reset Control Register (0E <sub>h</sub> )            |   |

| 7.5     | Exposer Gain A Register (10 <sub>h</sub> )           | 3 |

| 7.6     | Tristate Control Register (12 <sub>h</sub> )         | 3 |

| 7.7     | Column DOVA DC Register (20 <sub>h</sub> )           | 3 |

| 7.8     | Exposure GainB (21 <sub>h</sub> )                    |   |

| 7.9     | PGA Gain Mode (22 <sub>h</sub> )                     | 3 |

| 7.10    | ADC DOVA (23 <sub>h</sub> )                          | 3 |

| 7.11    | Capture Mode Control (40 <sub>b</sub> )              | 3 |

## **Technical Data**

## Kodak Digital Science KAC-1310 CMOS Image Sensor

| 7.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sub-sample Control (41 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 7.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TRIGGER and STROBE Control Register (42 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

| 7.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Programmable Window of Interest (WOI) (45 <sub>h</sub> -4C <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

| 7.15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Integration Time Control $(4D_h \rightarrow 4F_h)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                           |

| 7.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Programmable Virtual Frame $(50_h \rightarrow 53_h)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

| 7.17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SOF and VCLK Delay Registers (54 <sub>h</sub> and 55 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                           |

| 7.18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SOF & VCLK Width Register (56 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |

| 7.19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Readout Direction Register (50 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                           |

| 7.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Internal Timing Control Register (5F <sub>h</sub> and 60 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                           |

| 7.21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HCLK Delay Register (64 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

| 7.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Encoded Sync Register (65 <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |

| 7.23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mod64 Column Offset Correction Register (80 <sub>h</sub> -BF <sub>h</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                           |

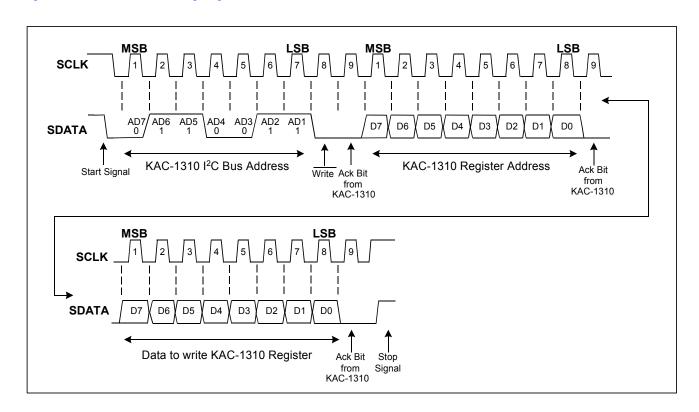

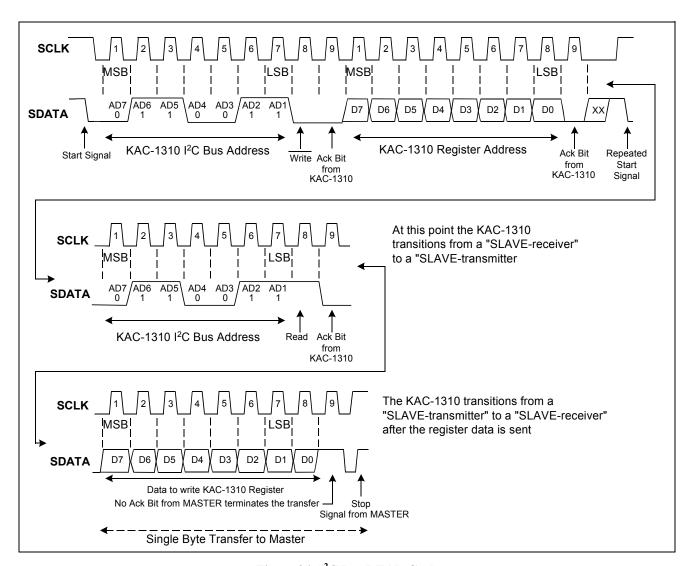

| 8.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sup>2</sup> C Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 8.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | KAC-1310 I <sup>2</sup> C Bus Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

| 8.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | START Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |

| 8.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Slave Address Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |